von Lukas Zeller

# HARDWARE-TIPS, INTERFACES

## Zu diesem Heft:

Damit einem dieses Heft etwas nützt, sollte man die Tips und Kniffe (oder etwas entsprechendes) kennen, etwas allgemeine Hardwarekenntnisse besitzen, und über die Service-Anleitung des PC-1500 verfügen.

#### Inhalt:

| 1. | Einleitung1                               |

|----|-------------------------------------------|

| 2. | Hardwarezustand des Rechners1             |

|    | 2.1 Speichervertellung1                   |

|    | 2.2 Vorhandene Decodierung2               |

| -  | 2.3 Bus-Timing, wichtige Prozessorsignale |

| -  | 2.4 Der I/O-Port LH-5810/11               |

| -  | 2.5 der 60-Pol Anschluss4                 |

| 3. | Schaltungsbeispiele4                      |

|    | 3.1 Decodierung4                          |

| -  | 3.2 Einfaches Parallelinterface5          |

|    | 3.3 Anschluss für MC-6800-Peripherie6     |

|    | 3.4 Speicherausbau                        |

|    | 3.5 Cassetteninterface                    |

| 4. | Bezugsquellen                             |

WWW. PC-1500 JNFO

Adresse: Lukas Zeller, Hofenstrasse 12, 8708 Männedorf

## 1.Einleitung

Der PC-1500 ist der erste echte 3-Bit Mikrocomputer im Taschenformat.Deshalb sind damit auch (prinzipiell) alle Interface-Möglichkeiten, die es auf "grossen" Mikros gibt, möglich. Wer aber ein Interface selbst bauen will, sei es well von SHARP das gewünschte Gerät nicht angeboten ist, oder well man das nötige Kleingeld z.B. zum Kauf eines RS-232-Interfaces nicht hat, der braucht einige Unterlagen. Erstens wäre da die Service-Anleitung des PC-1500 (erhältlich bei FACIT ADDO, Zürich, ca 15.-) zu erwähnen.Diese Investition lohnt sich bestimmt, da Schaltplan von Plotter und Rechner, die (hardwareseitige) Erklärung der wichtigsten IC's, Hinweise über das fachgerechte Zerlegen des PC-1500, Platinenlayouts (mehrfarbig) etc. enthalten sind.In meinen Blättern darf ich leider keine Schaltbilder o.ä. aus diesem Manual bringen, darum sollte man dieses besitzen. (Im Uebrigen: Auch die Kopie einer Kopie der Kopie des Originals ist meistens noch brauchbar...)

Als zweite Hilfe sind diese Seiten gedacht. Es werden keine fertigen Schaltungen gezeigt, sondern nur einzelne Teile. Damit sollte es möglich sein, eine Erweiterung nach eigenen Wünschen selbst zusammenzustellen.

Obwohl die neuen HCMOS und CMOS-IC's Immer robuster werden, ist eine gewisse Vorsicht zu empfehlen: Bei Lötarbeiten im Rechner sollte ein Kolben mit geerdeter Spitze verwendet werden. Auch müssen die Elkos vor dem Löten sicherheitshalber entleert werden (Ohne Batterien ALL RESET und ON 15 Sec. gedrückt halten!) Vor einem Eingriff vergegenwärtige man sich zudem, dass jegliche Garantien damit verfallen...

## Hardwarezustand des Rechners

#### 2.1 Speicherverteilung

Die Speicherverteilung im PC-1500 wird am besten mit einer Tabelle aufgezeigt: (Signalerklärungen s.unten)

| Υ0 |                            |    | 0000<br>3FFF                         | User-Memory (8K Modul<br>oder frei) |                                |

|----|----------------------------|----|--------------------------------------|-------------------------------------|--------------------------------|

| Y1 | so                         |    | 4000<br>47FF                         | User-Memory (2K Stand-<br>ard)      | TC 5517 oder<br>HM 6116 2048x8 |

|    | S1<br>S2<br>S3<br>S4<br>S5 |    | 4800<br>5000<br>5800<br>6000<br>6800 | User-Memory (4K oder<br>8K Modul)   |                                |

|    | SG                         |    | 7000<br>75FF                         | nicht ausdecodiert                  |                                |

|    |                            | V2 | 7600<br>76FF                         | Display Chip 1 und 3                | SC 882 G (2 StUck)             |

|    |                            | ٧3 | 7700<br>77FF                         | Display Chip 2 und 4                | SC 882 G (2 Stück)             |

|    | S7 | 7800 System-Speicher 7C00 System-Speicher 7FFF (nur READ III) | System-Spelcher                                  | TC 5514 (2 Stuck)                 |

|----|----|---------------------------------------------------------------|--------------------------------------------------|-----------------------------------|

|    |    |                                                               | System-Spelcher<br>(nur READ !!!)                |                                   |

| Y2 |    | 8000<br>BFFF                                                  | Systemerweiterung:<br>PV=1: Bank  <br>PV=2: Bank |                                   |

| Y3 |    | C000<br>FFFF                                                  | BASIC-Interpreter,<br>Betriebssystem             | 16384 x 8<br>SC 613128 F (1 Stück |

#### 2.2 Vorhandene Decodierung

Diese IC-Typen sind die schnelle CMOS-Version der altbekannten TTL-Serie.(SN74138,SN74139) Diese IC's nennen sich HCMOS und werden bald z.B. bei Motorola (Omni Ray,Zürich) erhältlich sein.Der 138-er ist ein 3-to-8-Decoder mit 3 Enable-Eingängen, der 139-er enthält 2 2-to-4-Decoder mit je einem Enableeingang (s.a.TTL-Datenblätter SN74138/9).In der Tabelle unter 2.1 sind die Decoder-Ausgänge (YO-Y3,SO-S7,V2,V3),die den entsprechenden Speicher anwählen,angegeben.(s.a. Schaltbild im Service-Manual) Der Port-Baustein LH5811 braucht keine externe Decodierung,da er 3 CS (Chip Select)-Eingänge hat.Damit belegt er die Adressen P-F000 bis P-FFFF (P=zweiter Speicherraum) Wichtig:

- Die Decoderausgänge YO bis Y3 sprechen in beiden Speicherräumen an.

- Die Decoderausgänge SO bis S7 sprechen nur im ersten Speicherblock an. Zusätlich wird die Decodierung nach dem Einschalten erst etwas verzögert freigegeben, damit die RAM-Inhalte nicht durch zufälligen Prozessorzugriff zerstört werden.

- Alle Decoderausgänge ausser V2 und V3 sind AKTIV LOW I

- V2 und V3 kommen nicht direkt vom TC40H139, sie werden mit Invertern AKTIV HIGH gemacht.

- Das PV-Signal wird nur wichtig, wenn man eigene BASIC-Befehle programmiert, da es nur im Raum zwischen 8000 und BFFF wirksam ist. (s.dazu Blätter "Funktionen und Prozeduren selbst programmieren.".)

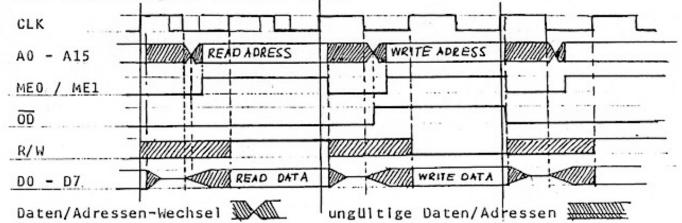

### 2.3 Bus-Timing.wichtige Prozessorsignale

Das Bus-Timing zeigt die zeitlichen Abläufe auf dem Systembus. Die genauen Zeitangaben fehlen leider, da sie nirgends angegeben sind und durch Messen keine genug genauen Ergebnisse erzielt werden konnten. Falls Sie einmal eine Busleitung ozilloskopieren, während der Rechner im BASIC-Eingabemodus läuft, werden Sie bemerken, dass die Leitung nur im Intervall von 5.5 ms während etwa 0.7 ms kurzzeitig aktiv ist, während sie in der übrigen Zeit auf LOW verharrt. Wird eine Taste gedrückt, so verlängern sich die aktiven Phasen auf bis zu ca. 3 ms, je nach Taste. Dies ist darauf zurückzuführen, dass die Eingaberoutine mit Start bei &E243 (s.Tips und Kniffe, Teil 2 S.5) mit Hilfe des Walt-Timers im I/O-Port 5810 den Prozessor softwaregesteuert in den genannten Intervallen anhält. Wahrscheinlich sinkt dabei der Stromverbrauch des Prozessors erheblich und trägt dazu bei, die Batterien zu schonen, wenn Rechenarbeit nicht bed-

tigt wird. Sobald aber ein Programm gestartet wird, sind die Bus-Leitungen dauernd aktiv, da nun der Rechner mit gösstmoglicher Geschwindigkeit arbeiten muss.

Tri-State (Ausgang Hochohmig, "High Z")

Zu den einzelnen Signalen:

- Clk: Sytemtakt, 1.3 MHz. Ein ganzer Buszyklus ist doppelt so lang wie ein Clk-Zyklus.

- A0 A15 : Adressbus.

- ME 0: Dieses Signal ist dann HiGH, wenn der Speicherblock 0 angewählt ist. (Normalspeicherbereich, durch PEEK und POKE adressierbar)

- ME 1: Dieses Signal ist dann HIGH, wenn der Speicherblock 1 angewählt ist. (Peripheriespeicherbereich, durch PEEK# und POKE# anwählbar)

- OD: Diese Leitung ist dann auf HiGH, wenn der Prozessor Daten in eine Speicherstelle einschreibt. Der Unterschied zu R/W besteht darin dass es invers ist, auch ist es vorher "valid" (= gültig), was in einigen Anwendungen von grosser Bedeutung ist.

- R/N: Dieses Signal gibt die Uebertragungsrichtung der Daten auf dem Datenbus an: HIGH= Prozessor liest, LOW= Prozessor schreibt. Im Gegensatz zu OD ist dieses Signal erst in der zweiten Bus-Zyklus-Hälfte "valid".

- <u>DO D7</u> bidirektionaler Datenbus, Richtung durch R/W und OD angegeben.

#### 2.4 Der 1/0-Port LH-5810/11

Dieses IC enthält drei parallele und einen Seriellen Port (s. Service-Anleitung). Für gewisse Anwendungen wichtig ist aber vorallem die Interrupt-Steuerung des IRQ-Prozessoreingangs, da hier das System einen User-Vektor zur Verfügung stellt (s.Tips und Kniffe, Memory-Map, &79DA). Zwei Register des Ports steuern den Interrupt:

Adresse P &FOOA Falls die folgenden Bits gesetzt sind, werden Interrupts vom betreffnden Eingang an den Prozessor weitergegeben:

Bit 0 IRQ- Eingang, mit Drucker an einen weiteren LH-5810/11 angeschlossen, sonst an der 60-Pol Leiste des PC-1500 verfügbar (IRQ).Genaueres s.unten.

- Bit 1 PB7-Eingang (BREAK-Taste)

Adresse &F00B Bits 0 und 1 zugeordnet wie in &F00A.Ein Bit wird gesetzt, wenn am dazugehörigen Eingang ein HIGH-Puls auftritt. Das Bit muss softwaremässig gelöscht werden.

Adresse &BOOA (nur mit CE-150) Steuerregister entsprechend &FOOA; Bedeutung der Bits:

- Bit 0 IRQ-Eingang an der 60-Pol-Leiste an der Rückseite des CE-150.

- Bit 1 PB7-Eingang (Papiervorschubtaste)

Adresse &B00B (nur mit CE-150) Flagregister entsprechend &F00B

Wichtig: Der IRQ-Ausgang des LH-5810/11 im PC-1500 geht direkt an den Prozessor. Der IRQ-Ausgang des LH-5810/11 im CE-150 jedoch geht an den IRQ-<u>Eingang</u> des Port-IC's im PC-1500.

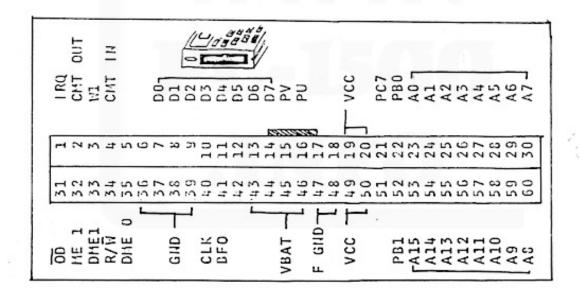

## 2.5 Der 60-Pol-Anschluss

Der 60-Pol-Anschluss beim PC-1500 und beim CE-150 sind beinahe Identisch.Die Unterschiede im folgenden:

- Die Ausgangsleitungen A0-A15, R/W, OD, ME1, DME0/1 sind Im CE-150 gepuffert, im PC-1500 jedoch nicht (direkt am LH-5801, nicht überlasten!)

- Der IRQ-Eingang geht an verschiedene Ports (s.oben)

- Die CMT-IN/OUT-Leitungen sind am CE-150-Anschluss nicht vorhanden.

## Schaltungsbeispiele

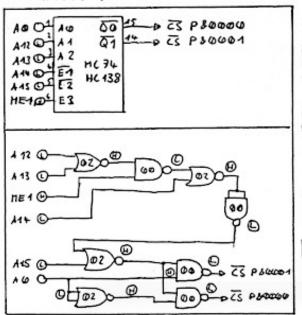

#### 3.1 Decodierung

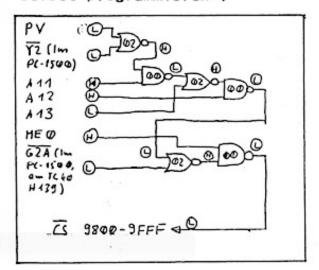

Zur Decodierung kann man die 3-to-8-Decoder MC74HC138 benützen, allerdings sind diese IC's im Moment noch schwer aufzutreiben. Darum sind auch Schaltungen mit den NAND und NOR-Gates MC74HC00/02 gezeigt.Die kleinen "H" und "L"-Symbole in Kreislein geben den Zustand der Leitung an, wenn die Decodierung anspricht.

1.Decodierung für Peripherieeinheit ;unvollständig decodiert.Adressen: P &0000 bis P &0FFF.

2.Decodierung für ein 2K-RAM

Typ HM-6116. Adressbereich

&9800 bis &9FFF.Das PV-Signal

wird berücksichtigt, da das

RAM im Systembereich liegt,

(s.dazu Heft "Funktionen

selbst programmieren")

#### 3.2 Einfaches Parallelinterface

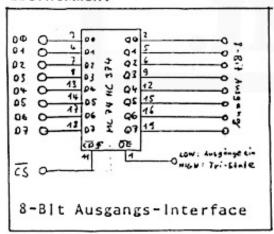

Die Anforderungen an ein Parallelinterface sind etwa folgende: Ausgangsleitungen mit Latch (Damit die Daten bis zum nächsten Prozessorzugriff an den Ausgängen erhalten bleiben, Eingangs-leitungen durch einfachen LD-Befehl abfragbar. Für die Ausgänge übernimmt ein 8-Bit Latch (D-Type-Flip-Flop) vom Typ MC74HC374 die Speicherung; zusätzlich bietet dieser Baustein Tri-State-Ausgänge. Bei der positiven Flanke des CS-signals (s.3.1) werden die Daten vom Datenbus in die Flip-Flops übernommen:

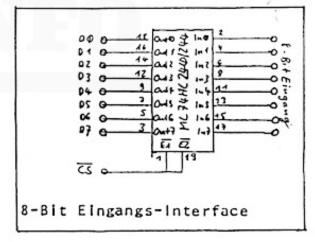

Der Eingangsteil des Parallelinterfaces benutzt einen Tri-State Buffer Typ MC74HC240/244. Bei der Verwendung des MC74HC240 werden die Eingangsleitungen invertiert, beim MC74HC244 nicht. Der Zustand der Eingangsleitungen wird dann auf den Datenbus geschaltet, wenn das CS-Signal auf O geht.(Schaltung s.oben)

#### 3.3 Anschluss für MC-6800-Peripherie

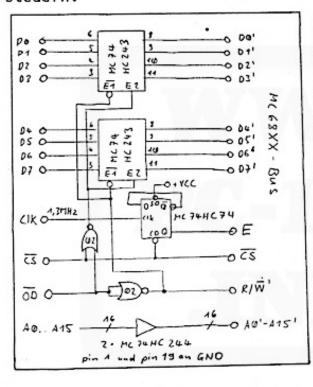

Die einfachen Interface-Schaltungen wie Parallelinterface kann man gut mit normalen HCMOS-Logikbausteinen aufbauen. Für kompliziertere Interface-Aufgaben (Serielle Datenübertragung, TV-Interface) ist dies kaum mehr möglich. Da derartige Interfaces meistens nicht mobil sein müssen und darum auch eine Netzstromversorgung eingebaut werden kann, liegt es nahe, die normalen NMOS-Peripheriebausteine, wie sie für "grosse" Computer verwendet werden, zu benützen. Da Ich mich nur in der Motorola-Peripherie auskenne, beschränke Ich mich auf die Beschreibung eines Anschlusses dieser Bausteine an den PC-1500. Wahrscheinlich wäre INTEL-Peripherie auch geeignet. Bei allen Arten von NMOS-Bausteinen ist jedoch zu beachten, dass alle Signale über ein Buffer-IC geführt werden (z.B.MC74HC241), damit der CMOS-Bus des Prozessors nicht überlastet wird.Die folgende Schaltung hat die Aufgabe, das E und das R/W-Signal (R/W des LH 5801 kommt zu spät) zu erzeugen und den Datenbus-Buffer zu steuern:

Diese Schaltung kann mit allen statischen Bausteinen der 68XX-Serie (Bausteine die kein permanentes E-Signal brauchen) verwendet werden. Die IRQ-Ausgänge können direkt an den IRQ-Eingang des PC-1500 angeschlossen werden.

#### Geeignete Bausteine:

MC 6821 PIA (parallel :2\*8) MC 6850 ACIA (seriell) MC 6845 CRTC (Videointerf.) MC 6847,Y (Video farbig)

Der PTM (programmierbarer Timer) kann auch verwendet werden,jedoch fehlt wegen dem

nich dauernden E-Signal die

Interne Taktquelle.

Genaueres über die genannten

IC's siehe Motorola Datenbuch

"microcomputer components"

Bei der Verwendung der 68XX-IC's denke man an eine ausreichende externe Stromversorgung. Mit dieser Schaltung steht dem PC-1500 der Weg zu allen Peripherien offen, sofern sie nicht zu schnelle Przessorarbeit erfordern, wie z.B Floppy Disk.

#### 3.4 Speicherausbau

Dank den neuen 2 K \* 8 Bit statischen RAH's ist die Erhöhung der Speicherkapazität eigentlich kein Problem. Am besten verwendet man die kleinen FLAT-PAC-Ausführungen (z.B.HM 6116 LPF5) da sich diese gut in den Rechner einbauen lassen. Wenn man die IC's in den PC-1500 hineinbaut, so schaltet man sie am besten mit dem schon vorhandenen 6116 (bzw.TC5517) parallel, bis auf den CS-Eingang natürlich, den man an eine geeignete Decodierung anschliesst (s.3.1). Bei geschickter Anordnung kann der Speicher auf 28KByte BASIC erweitert werden; alles im PC-1500 ein-

gebaut.

#### 3.5 Cassetteninterface

Wer keinen Drucker CE-150 hat, entweder aus finanziellen Gründen oder weil man ihn nicht braucht, wird auch das Cassetteninterface vermissen, da man dieses nicht separat kaufen kann. Dem lässt sich abhelfen:

Man baut sich ein RAM in den Speicherbereich von &B800 bis &BFFF ein. Dann baut man sich die kleine Schaltung, die man in der Secvice-Anleitung findet, nach. (Aus Copyright-Gründen kann ich diese hier nicht veröffentlichen). Das einzige Problem besteht nun darin, die Software aus einem (ausgeliehenen) CE-150 in den eigenen Rechner zu transportieren. Der CE-150 darf ja nicht angeschlossen werden, solange das RAM im Bereich von &B800 bls &BFFF ist, sonst Überlappen sich die Speicher. Die Lösung geht so: Man lötet den CS-Eingang des RAMs am Anfang nicht an der vorgesehenen Decodierung, sondern am S5-Ausgang des TC40H138 an.Dann transportiert man mit angeschlossenem CE-150 die Software der Cassettensteuerung (&B800 bis &BFFF) nach &6800 bis &6FFF (dort ist das RAM im Moment ). Danach muss man den PC-1500 vom CE-150 wegnehmen und nocheinmal Offnen, diesmal aber tut man die Batterien sofort wieder hinein nachdem man die Schrauben im Batteriefach gelöst hat. Dadurch bleibt die Software erhalten. Nun muss man den CS an die vorgesehene Decodierung anschliessen. Da dies mit eingesetzten Batterien geschieht (Rechner natürlich ausgeschaltet), muss man besonders aufpassen. Danach muss man nur noch die Schaltung aus der Service-Anleitung an CMT IN/OUT und die Stromversorgung anschliessen, und schon hat man ein Cassetten-interface mit allen Schi kanen. Wenn man auch noch den R/W-Pin des RAMs direkt mit VCC verbindet, ist die Software auch vor Ueberschreiben geschützt.

Dies alles tönt etwas "kriminell", doch man kommt auf diesem Weg billig zu einem Cassetteninterface.

#### 4.Bezugsquellen

Die 60-pol Steckerleiste ist bei FACIT ADDO in Zürich erhältlich, wie auch die Service-Anleitung.

Die Motorola IC's sind bei OMNI RAY in Zürlch erhältlich.

Die HM 6116 LPF3 sind bei FENNER in Sissach erhältlich.

## SOFTWARE DES CE-158 (RS-232C und Centronics)

## 1.Einleitung

Die Software des CE-158 befindet sich im 8K-langen Bereich von &8000 bis &9FFF. Da die Software aber 16 K umfasst, wird der Bereich durch das PU-Prozessorsignal in zwei "Banks" aufgeteilt. Daher beachte man, dass zum Aufruf eines Unterprogramms dieses Signal richtig geschaltet ist.

Diese Beschreibung zeigt nur die wichtigsten Routinen, die zur Ansteuerung der im CE-158 enthaltenen Schnittstellen von der Maschinensprache aus notwendig sind.

## Memory-Map

Zellenlänge für RS-232C &7852 Zellenlänge für CENTRONICS &7853 Zeichenzähler für RS-232C &7854 Zeichenzähler für CENTRONICS 5 **&7855** 4 Zweites Zeichen Bits 0..2 entsprechend des Endcodes: Bits 4..6 doch für 00=kein zweites RS-232C-Schnittstelle Zeichen 01=CR → PU-flag (gibt beim BASIC-10=LF Betrieb den PU-Zustand an) Erstes Zeichen des Endcodes: 0=CR, 1=LF CENTRONICS RS-232 C

&789E (liegt im Speicherbereich des Output-Buffers)

Schnittstellenwahl: - CO für RS-232 C

- C4 für CENTRONICS

(Die Werte entsprechen den OPN-Codes von "COM" und "LPRT")

&7BAl Bit 6 getestet von SBR &9BAA (s.dort)

## Unterprogramme

PUO: &93CB Erzeugt ERROR 27, wenn nicht OPN "COM" gemacht

worden ist.

PUO: &93C1 Erzeugt ERROR 27, wenn nicht OPN "LPRT" gemacht

worden ist.

PUO: &98B7 Erstellt einen Parameterblock für die jeweils eingestellte Schnittstelle, der &A Bytes umfasst und ab &7BA6 abgelegt wird:

Zeichen Zeichen- Endc.2 Endc.1 Direkt indirekt per Zei- zähler Zugriff Zugriff Vektor Vektor

&7BA6 &7BA7 &7BA8 &7BA9 &7BAA &7BAD

#### Dazu Erläuterungen:

Je nach dem Wert in &7B9E wird der Parameterblock für die RS-232 oder Centronics-Schnittstelle erzeugt.

Die ersten zwei Bytes entsprechen den Werten, die in &7851/2 bzw. &7853/4 abgespeichert sind.

Die zwei Bytes für den End-Code enthalten entweder CR (&D) oder LF (&A). Anstatt des zweiten END-Codes kann auch 0 stehen --> kein 2.Endcode.

Die darauffolgenden 6 Bytes sind zwei JMP-Befehle, die zur Ansteuerung der Hardware angesprungen werden müssen:

- a) beim CENTRONICS-Interface: Das A-Register muss vor dem Aufruf dieser Routine den Wert &6C enthalten haben, damit ein gültiger Parameterblock erzeugt wird.

- erster JMP-Vektor: Das im A-Register stehende Zeichen wird direkt ausgegeben (Zeichenzähler nicht verändert). ist beim Rücksprung das C-Flag gesetzt, so enthält ZH den Code des entstandenen ERROR's; ist ZH=0 so bedeutet das, dass die BREAK-Taste gedrückt wurde.

- zweiter JMP-Vektor: Das im durch X addressierte Byte wird ausgegeben, der Zeichenzähler erhöht und am Zeilenende automatisch die oder der gewählte(n) Endcode(s) ausgegeben. Das X-Register wird um 1 erhöht. Ist das C-Flag gesetzt, so bedeutet dies dasselbe wie beim ersten Vektor.

- b) beim RS-232-interface:

Wenn das A-Register den Wert & GA enthält, so sind die zwei

JMP-Vektoren für Ausgabe vorbereitet. Die Funktion ist dann

dieselbe wie beim CENTRONICS-interface (s.oben)

Wenn das A-Register den Wert &OC enthält, so sind die zwei JMP-Vektoren für Eingabe vorbereitet.

Der erste Vektor ruft ein Unterprogramm auf, das ein Zeichen vom RS-232-Interface ins A-Register einliest. Ist beim Rücksprung das C-flag gesetzt, so enthält ZH die ERROR-Nummer, wenn ZH=0 ist, wurde die BREAK-Taste gedrückt.

Der zweite Vektor ruft ein Unterprogramm auf, das ein Zeichen einliest, und es an der durch X angegebenen Adresse ablegt. Das X-Register wird anschliessend um 1 erhöht. Ist das eingelesene Zeichen ein CR (&OD) und ist das Bit 2 in &7BA1 gesetzt, so ist beim Rücksprung das C-Flag gesetzt und ZH enthält den Wert &3E. Ist das C-Flag bei einem anderen Wert von ZH gesetzt, so bedeutet dies dasselbe wie beim ersten Vektor.

- &9BAA Falls Bit 6 in &7BA1 gesetzt ist, so wird der Wert des Zeichenzählers im Parameterblock (&7BA7) nach &7853 oder &7854 zurückgespeichert,je nach dem, welcher Tell des Interfaces durch den Wert in &7B9E angewählt ist.

- &9841 Mit SBR &9887 muss zuvor der Parameterblock vorbereitet worden sein. Es wird ein End-Code ausgegeben, und der Zeichenzähler im Parameterblock auf null gesetzt.